Silicon carbide (SiC) has emerged as a critical material in the development of next-generation power and high-frequency electronic devices due to its wide bandgap, high breakdown electric field, and excellent thermal conductivity. The wafer processing workflow of SiC is considerably more complex than that of traditional silicon, requiring stringent control over crystal quality, defect management, and high-precision fabrication techniques. This article outlines the key stages involved in SiC wafer processing, from epitaxial growth to final device fabrication.

1. Substrate Preparation

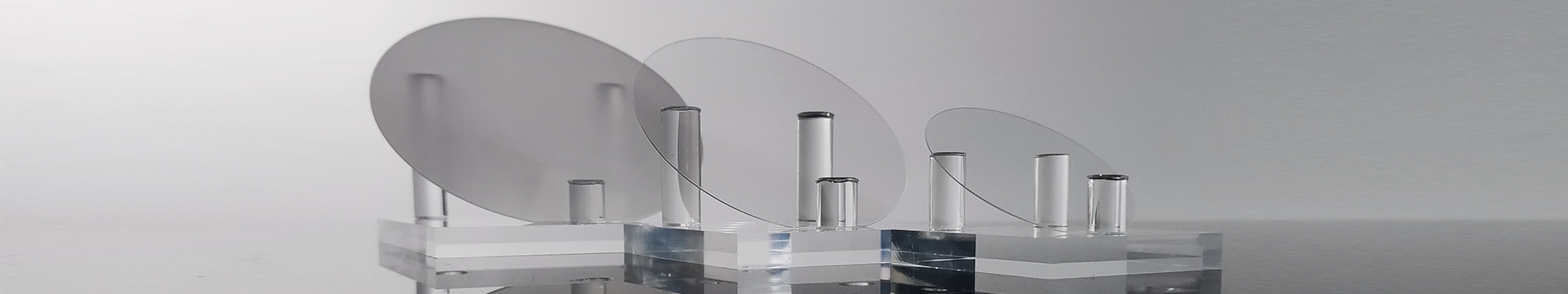

The SiC wafer fabrication process begins with high-quality, monocrystalline SiC substrates, typically in 4H-SiC or 6H-SiC polytypes. Substrate preparation is crucial to ensuring uniform epitaxial growth and device reliability.

Key steps include:

-Surface Polishing: Chemical Mechanical Polishing (CMP) is used to achieve atomic-level flatness and minimal surface roughness, which is essential for defect-free epitaxy.

-Contamination Removal: Wet and dry cleaning techniques are employed to eliminate organic residues, particles, and metal contaminants.

-Orientation Control: Substrate orientation (typically <0001>) is precisely maintained to optimize epitaxial growth and electronic performance.

2. Epitaxial Growth

The epitaxial growth stage involves depositing a high-purity, lightly doped SiC layer onto the substrate, forming the active region for device structures. This is most commonly performed using Chemical Vapor Deposition (CVD), specifically Horizontal or Vertical Hot-Wall CVD.

Epitaxy process characteristics:

-Thickness Range: From a few micrometers (for RF devices) to over 100 µm (for high-voltage devices).

-Doping Control: N-type (nitrogen-doped) or P-type (aluminum or boron-doped) layers are introduced to engineer specific electronic properties.

-Defect Minimization: High attention is paid to suppressing stacking faults, basal plane dislocations (BPDs), and micropipes.

3. Wafer Slicing and Surface FinishingAfter epitaxial growth, SiC ingots or wafers are sliced and further processed: -Wafer Slicing: Wire saws with diamond-coated wires are used to slice SiC boules into wafers. The process must manage the hardness and brittleness of SiC to avoid chipping and microcracks.

-Grinding and Lapping: These steps reduce thickness variation and improve flatness.

-Final Polishing: Achieves mirror-finish surfaces with sub-nanometer roughness, ready for lithography.

4. Photolithography and MaskingPhotolithography is used to transfer intricate circuit patterns onto the wafer surface. It includes:

-Photoresist Coating: Uniform application of light-sensitive resist.

-Mask Alignment and Exposure: Ultraviolet (UV) light is used to expose the wafer through a photomask.

-Development: Removes the exposed or unexposed regions (depending on resist type), leaving behind the desired pattern.

Precision in alignment and resolution is critical due to the high-density integration and small feature sizes in modern SiC devices.

5. EtchingFollowing patterning, selective material removal is carried out through etching:

-Dry Etching (Plasma or RIE): Enables anisotropic and high-aspect-ratio etching required for vertical device architectures.

-Wet Etching: Less commonly used due to limited selectivity and control, but applicable in some cases for material smoothing.

SiC's chemical inertness demands robust etch chemistries, often involving fluorine-based plasmas.

6. Doping and ActivationTo tailor electrical characteristics, specific regions of the SiC wafer are doped: -Ion Implantation: High-energy ions (e.g., Al⁺, N⁺) are implanted into the wafer to form P-N junctions or channel regions.

-Annealing: Post-implantation thermal annealing at temperatures often exceeding 1600 °C is required to activate dopants and repair lattice damage.

The high-temperature stability of SiC enables dopant activation without melting or degrading the substrate.

7. Metallization and Contact FormationCreating ohmic and Schottky contacts is vital for device function:

-Metal Deposition: Techniques such as sputtering, evaporation, or CVD deposit metal layers (e.g., Ni, Al, Ti).

-Contact Annealing: Ensures formation of low-resistance ohmic contacts, especially for power devices.

-Interconnects: Metallization layers are patterned to form the circuit interconnects between active regions.

Barrier layers and passivation may also be introduced to prevent metal diffusion and ensure device stability.

8. Device Fabrication and PackagingAt this stage, fully functional devices such as MOSFETs, Schottky diodes, or Junction Barrier Schottky (JBS) diodes are completed. Key processes include:

-Die Separation: Wafers are diced into individual chips.

-Packaging: Devices are encapsulated in high-reliability packages, often with advanced thermal management solutions to support SiC’s high-temperature capabilities.

-Electrical Testing: Each device undergoes characterization to validate parameters such as breakdown voltage, leakage current, and switching speed.

ConclusionSiC wafer processing is a multidisciplinary, high-precision workflow that spans substrate engineering, epitaxial growth, microlithography, doping, and final device integration. While the technical challenges are significant—owing to the material’s hardness, chemical resistance, and defect sensitivity—the performance benefits in high-power, high-temperature, and high-frequency applications are unmatched.

As demand for energy-efficient electronics continues to rise, especially in sectors like electric vehicles, renewable energy, and 5G communications, the strategic value of SiC wafer processing will only grow—making it a cornerstone of modern semiconductor technology.